# ezv technologies

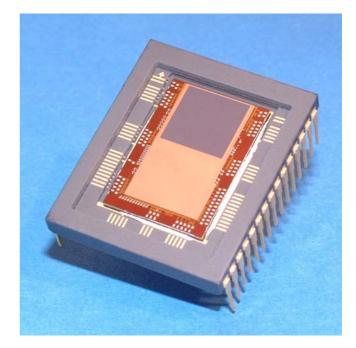

## CCD97–00 Front Illuminated 2-Phase IMO Series Electron Multiplying CCD Sensor

#### INTRODUCTION

The CCD97 is part of the new L3Vision<sup>®</sup> range of products from e2v technologies. This device uses a novel output amplifier circuit that is capable of operating at an equivalent output noise of less than one electron at pixel rates of over 11 MHz. This makes the sensor well suited for scientific imaging where the illumination is limited.

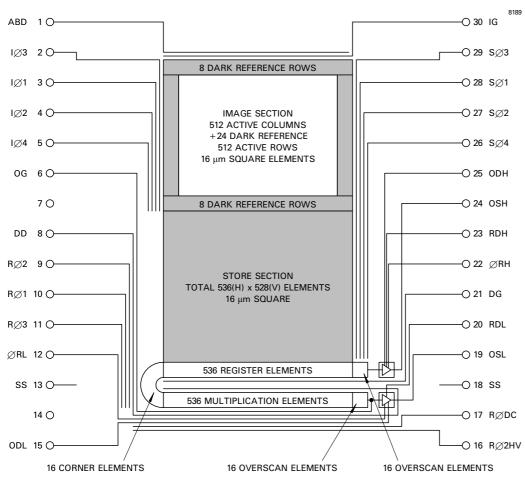

The sensor is a frame transfer device and can operate in inverted mode to suppress dark current as this is now the dominant noise source (even at high readout rate). The image and store sections are designed to operate in 2-phase mode, to maximise the highest achievable parallel transfer frequency.

The sensor functions by converting photons to charge in the image area during the integration time period, then transferring this charge through the image and store sections into the readout register. Following transfer through the readout register, the charge is multiplied in the gain register before conversion to a voltage by an output amplifier.

The sensor has two output amplifiers; a low noise, high responsivity output for normal CCD operation and a large signal amplifier for when multiplication gain is employed.

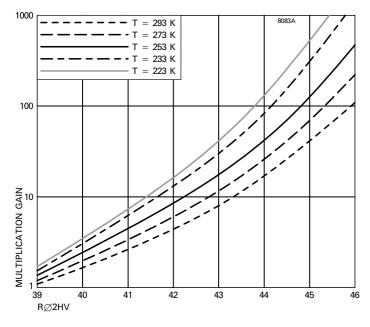

Operation of the high gain mode is controlled by adjustment of the multiplication phase amplitude  $R\emptyset$ 2HV.

A variant exists to supply devices with a lumogen coating, to enhance UV response.

#### **GENERAL DATA**

| Active image area 8.192 x 8.192 mm | n  |

|------------------------------------|----|

| Image section active pixels        | /) |

| Image pixel size                   | n  |

| Number of output amplifiers        | 2  |

| Fill factor                        | 6  |

| Additional dark reference columns  | 4  |

| Additional overscan rows           | 6  |

| Spectral range                     | n  |

#### PACKAGE DETAILS (see Fig. 15)

#### Ceramic Package

| Overall dimensions  |    |    |      |     |     |     |  |  | 28 | x 22 | 2.86 | mm  |

|---------------------|----|----|------|-----|-----|-----|--|--|----|------|------|-----|

| Number of pins .    |    |    |      |     |     |     |  |  |    |      |      | 30  |

| Inter-pin spacing   |    |    |      |     |     |     |  |  |    | 1    | 778  | mm  |

| Opposite row spaci  | ng |    |      |     |     |     |  |  |    | 2    | 2.86 | mm  |

| Mounting position   |    |    |      |     |     |     |  |  |    |      |      | any |

| The pin 1 marker is | sh | ow | n ii | n F | ig. | 15. |  |  |    |      |      |     |

## STORAGE AND OPERATION TEMPERATURE EXTREMES

|                              | MIN   | MAX   |

|------------------------------|-------|-------|

| Storage temperature (°C)     | - 200 | + 100 |

| Operating temperature (°C)   | - 120 | + 75  |

| Temperature ramping (°C/min) | -     | 5     |

**Note:** Operation or storage in humid conditions may give rise to ice on the sensor surface on cooling, causing irreversible damage.

e2v technologies limited, Waterhouse Lane, Chelmsford, Essex CM1 2QU England Telephone: +44 (0)1245 493493 Facsimile: +44 (0)1245 492492 e-mail: enquiries@e2vtechnologies.com Internet: www.e2vtechnologies.com Holding Company: e2v holdings limited

e2v technologies inc. 4 Westchester Plaza, PO Box 1482, Elmsford, NY10523-1482 USA Telephone: (914) 592-6050 Facsimile: (914) 592-5148 e-mail: enquiries@e2vtechnologies.us

#### **TYPICAL PERFORMANCE SPECIFICATIONS**

Except where otherwise specified, the following are measured for operation at a pixel rate of 11 MHz, with typical operating voltages. Parameters are given at 223 K unless specified otherwise. Where parameters are different in the normal and high gain mode, both are given.

| PARAMETER                                                                             | UNIT                    | MIN | TYPICAL    | MAX  |

|---------------------------------------------------------------------------------------|-------------------------|-----|------------|------|

| Output amplifier responsivity, HR amplifier (normal mode) (see note 1)                | µV/e−                   | -   | 5.3        | -    |

| Output amplifier responsivity, LS amplifier (normal mode) (see note 1)                | µV/e−                   | -   | 1.1        | -    |

| Multiplication register gain, LS amplifier (high gain mode)<br>(see notes 2, 3 and 4) |                         | 1   | -          | 1000 |

| Peak signal - 2-phase IMO                                                             | e <sup>-</sup> /pixel   | 90k | 130k       | -    |

| Charge handling capacity of multiplication register (see note 5)                      | e <sup>-</sup> /pixel   | -   | 800k       | -    |

| Readout noise at 50 kHz with CDS, HR amplifier (normal mode) (see note 6)             | e <sup>-</sup> rms      | -   | 2.2        | -    |

| Readout noise at 1 MHz with CDS, HR amplifier (normal mode) (see note 6)              | e <sup>-</sup> rms      | -   | 5.4        | -    |

| Amplifier reset noise (without CDS), HR amplifier (normal mode) (see note 6)          | e <sup>-</sup> rms      | -   | 50         | -    |

| Readout noise at 50 kHz with CDS, LS amplifier (normal mode) (see note 6)             | e <sup>-</sup> rms      | -   | 6          | -    |

| Readout noise at 1 MHz with CDS, LS amplifier (normal mode) (see note 6)              | e <sup>-</sup> rms      | -   | 14         | -    |

| Amplifier reset noise (without CDS), LS amplifier (normal mode) (see note 6)          | e <sup>-</sup> rms      | -   | 120        | -    |

| Readout noise at 1 MHz (high gain mode) (see note 6)                                  | e <sup>-</sup> rms      | -   | <1         | -    |

| Maximum frequency (settling to 1%), HR amplifier (see notes 6 and 7)                  | MHz                     | -   | -          | 3    |

| Maximum frequency (settling to 5%), HR amplifier (see notes 6 and 7)                  | MHz                     | -   | -          | 4.5  |

| Maximum frequency (settling to 1%), LS amplifier (see note 6 and 7)                   | MHz                     | -   | -          | 9    |

| Maximum frequency (settling to 5%), LS amplifier (see note 6 and 7)                   | MHz                     | -   | -          | 15   |

| Maximum parallel transfer frequency (see note 1)                                      | MHz                     | -   | 1.6        | -    |

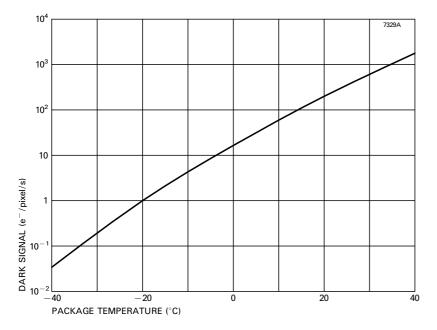

| Dark signal at 293 K (see note 8)                                                     | e <sup>-</sup> /pixel/s | -   | 160        | 320  |

| Dark signal non-uniformity (DSNU) at 293 K (see note 9)                               | e <sup>-</sup> /pixel/s | -   | 60         | -    |

| Excess noise factor (see note 10)                                                     |                         | -   | $\sqrt{2}$ | -    |

#### NOTES

- 1. Measured at a pixel rate of 1 MHz.

- 2. The typical variation of gain with  $R\emptyset$  2HV is shown in Fig. 1.

- 3. The variation of gain with  $R\emptyset 2HV$  at different temperatures is shown in Fig. 1.

- 4. Some increase of RØ2HV may be required throughout life to maintain gain performance. Adjustment of RØ2HV should be limited to the maximum specified under Operating Conditions.

- 5. When multiplication gain is used, a linear response of output signal with input signal is achieved for output signals up to 400 ke<sup>-</sup> typically.

- 6. These values are inferred by design and not measured.

- 7. The quoted maximum frequencies assume a 20 pF load and that correlated double sampling is being implemented. If, instead, single sampling is used, the output will be settled to 1% at 15 MHz typically.

- 8. The quoted dark signal has the usual temperature dependence for inverted mode operation. For operation at high frame rates with short integration times, there will also be a significant component generated during readout through the register. Operating at a temperature of 293 K and 30 Hz frame rate, the readout component contributes 4 e<sup>-</sup>/pixel/frame typically, at a gain of 1000 and referenced to the image area, and has a temperature dependence consistent with non-inverted mode operation.

There exists a further weakly temperature dependent component, the clock induced charge, which is independent of the integration time. The clock induced charge is dependent on the operating biases and timings employed and is typically 0.1 e<sup>-</sup>/ pixel/frame at T = -55 °C.

- For more information, refer to the technical note "Dark Signal and Clock-Induced Charge in L3Vision<sup>TM</sup> CCD Sensors".

- 9. DSNU is defined as the  $1\sigma$  variation of the dark signal.

- 10. The excess noise factor is defined as the factor by which the multiplication process increases the shot noise on the image when multiplication gain is used.

#### DEVICE COSMETIC PERFORMANCE

Grade 1 devices are supplied to the blemish specification shown below.

Note that incorrect biasing of the device may result in spurious dark or white blemishes appearing. These will be eliminated if the biases are adjusted.

#### **Test Conditions**

| Operating mode      | Devices run in 2-phase inverted mode, with an integration time of 30 ms and a readout rate of 11 MHz. |

|---------------------|-------------------------------------------------------------------------------------------------------|

| Sensor temperature  | 18 ± 3 °C.                                                                                            |

| Multiplication gain | Set to approximately 1000.                                                                            |

| Illumination        | Set to give a signal level of approximately 30 e <sup>-</sup> /pixel/frame.                           |

#### **BLEMISH SPECIFICATION**

| Black Columns    | Black defects are counted when they have a responsivity of less than 80% of the local mean signal at approximately the specified multiplication gain and level of illumination. A black column contains at least 9 black defects.                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| White Columns    | White defects are pixels having a dark signal generation rate corresponding to an output signal of greater than 5 times the maximum dark signal level. A white column contains at least 9 white defects.                                                                                                                                                                                                                  |

| Pin-Head Columns | Pin-head columns are manifest as a partial dark column with a bright pixel showing photoresponse<br>at the end of the column nearest to the readout register. Pin-head columns are counted when the<br>black column has a responsivity of less than 80% of the local mean signal at approximately the<br>specified multiplication gain and level of illumination. A pin-head column contains at least 9 black<br>defects. |

#### SPECIFICATION

| PARAMETER                | GRADE 1 SPECIFICATION | <b>GRADE 2 SPECIFICATION</b> |

|--------------------------|-----------------------|------------------------------|

| White Columns            | 0                     | 0                            |

| Black / Pin-head Columns | 0                     | 2                            |

#### **ORDERING INFORMATION**

| PART NUMBER       | OPERATING MODE | COATING | WINDOW    |

|-------------------|----------------|---------|-----------|

| CCD97-00-*- (TBC) | 2-phase        | None    | Temporary |

| CCD97-00-*- (TBC) | 2-phase        | UV      | Temporary |

\* denotes grade of device.

# Figure 1: TYPICAL VARIATION OF MULTIPLICATION GAIN WITH $R \ensuremath{\not \oslash} 2 \text{HV}$ AT DIFFERENT TEMPERATURES

Figure 2: TYPICAL VARIATION OF DARK SIGNAL WITH TEMPERATURE

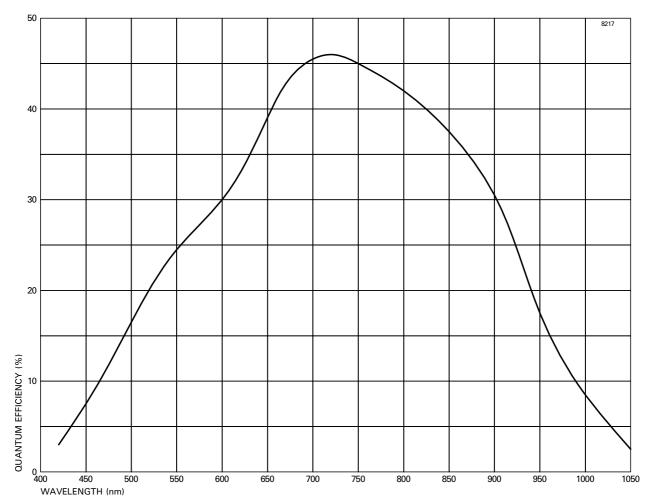

## Figure 3: TYPICAL SPECTRAL RESPONSE (At -20 °C, no window, no coating)

#### **ABSOLUTE MAXIMUM RATINGS**

Maximum ratings are with respect to SS.

| PIN | CONNECTION | MIN (V) | MAX (V) |

|-----|------------|---------|---------|

| 1   | ABD        | -0.3    | + 25    |

| 2   | IØ3        | -20     | + 20    |

| 3   | IØ1        | -20     | + 20    |

| 4   | IØ2        | -20     | + 20    |

| 5   | IØ4        | -20     | + 20    |

| 6   | OG         | -20     | + 20    |

| 7   | n.c.       |         |         |

| 8   | DD         | -0.3    | + 25    |

| 9   | RØ2        | - 20    | + 20    |

| 10  | RØ1        | -20     | + 20    |

| 11  | RØ3        | -20     | + 20    |

| 12  | ØRL        | -20     | + 20    |

| 13  | SS         | (       | )       |

| 14  | n.c.       |         |         |

| 15  | ODL        | -0.3    | + 32    |

| 16  | RØ2HV      | - 20    | + 50    |

| 17  | RØDC       | - 20    | + 20    |

| 18  | SS         | (       | )       |

| 19* | OSL        | -0.3    | + 25    |

| 20  | RDL        | -0.3    | + 25    |

| 21  | DG         | - 20    | + 20    |

| 22  | ØRH        | - 20    | + 20    |

| 23  | RDH        | -0.3    | + 25    |

| 24* | OSH        | -0.3    | + 25    |

| 25  | ODH        | -0.3    | + 32    |

| 26  | SØ4        | - 20    | + 20    |

| 27  | SØ2        | - 20    | + 20    |

| 28  | SØ1        | - 20    | + 20    |

| 29  | SØ3        | -20     | + 20    |

| 30  | IG         | - 20    | + 20    |

n.c. not connected.

\* Permanent damage may result if, in operation, OSL or OSH experience short-circuit conditions.

#### Maximum voltages between pairs of pins:

| PIN  | CONNECTION          | PIN | CONNECTION | MIN<br>(V) | MAX<br>(V) |

|------|---------------------|-----|------------|------------|------------|

| 24   | OSH                 | 25  | ODH        | — 15       | + 15       |

| 19   | OSL                 | 15  | ODL        | — 15       | + 15       |

| 16   | RØ2HV               | 17  | RØDC       | -20        | + 50       |

| 16   | RØ2HV               | 11  | RØ3        | -20        | + 50       |

| Outp | ut transistor curre |     | 20         |            |            |

#### **ESD HANDLING PROCEDURES**

CCD sensors, in common with most high performance IC devices, are static sensitive. In certain cases a static electricity discharge may destroy or irreversibly degrade the device. Accordingly, full anti-static handling precautions should be taken whenever using a CCD sensor or module. These include:

- Working at a fully grounded workbench.

- Operator wearing a grounded wrist strap.

- All receiving socket pins to be positively grounded.

- Unattended CCDs should not be left out of their conducting foam or socket.

All devices are provided with internal protection circuits to most gate electrodes but not to the other pins.

Evidence of incorrect handling will terminate the warranty.

#### **EXPOSURE TO RADIATION**

Exposure to radiation may irreversibly damage the device and result in degradation of performance. Users wishing to operate the device in a radiation environment are advised to consult e2v technologies.

#### **OPERATING CONDITIONS**

Typical operating voltages are as given in the table below. Some adjustment within the minimum-maximum range specified may be required to optimise performance.

| CONNECTION     | PULSE AMPLITUDE OR DC LEVEL (V) |         |                  |  |  |  |  |

|----------------|---------------------------------|---------|------------------|--|--|--|--|

|                | Min                             | Typical | Max              |  |  |  |  |

| IØ1,2,3,4 high | +5 (see note 11)                | +7      | +9 (see note 11) |  |  |  |  |

| IØ1,2,3,4 low  | -6                              | -5      | -4               |  |  |  |  |

| SØ1,2,3,4 high | +5 (see note 11)                | +7      | +9 (see note 11) |  |  |  |  |

| SØ1,2,3,4 low  | -6                              | -5      | -4               |  |  |  |  |

| RØ1,2,3 high   | +8                              | + 12    | + 13             |  |  |  |  |

| RØ1,2,3 low    | -                               | 0       | -                |  |  |  |  |

| RØ2HV high     | + 20                            | + 40    | +50 (see note 4) |  |  |  |  |

| RØ2HV low      | 0                               | +4      | +5               |  |  |  |  |

| ØRL, ØRH high  | see note 12                     | + 10    | see note 12      |  |  |  |  |

| ØRL, ØRH low   | -                               | 0       | -                |  |  |  |  |

| RØDC           | +2                              | + 3     | +5               |  |  |  |  |

| OG             | +1                              | + 3     | +5               |  |  |  |  |

| IG             | -                               | -5      | -                |  |  |  |  |

| SS             | 0                               | +4.5    | +7               |  |  |  |  |

| ODL, ODH       | + 25                            | + 28    | + 32             |  |  |  |  |

| RDL, RDH       | + 15                            | + 17    | + 20             |  |  |  |  |

| ABD            | + 10                            | + 18    | + 20             |  |  |  |  |

| DG low         | -                               | 0       | -                |  |  |  |  |

| DG high        | + 10                            | + 12    | + 13             |  |  |  |  |

| DD             | + 20                            | + 24    | + 25             |  |  |  |  |

#### NOTES

11. IØ and SØ adjustment may be common.

- 12.  $\emptyset$ RL and  $\emptyset$ RH high level may be adjusted in common with R $\emptyset$ 1,2,3.

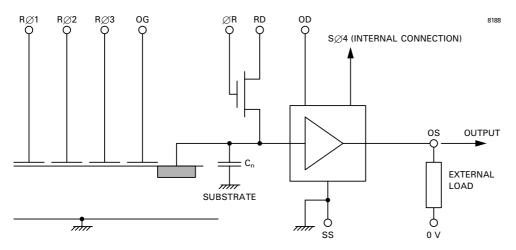

- 13. Other than the output gates (OG), there are no common connections made between the two amplifiers, and either can be powered down by connecting the appropriate output drain (OD) connection to substrate (SS). The reset drains (RD) should remain biased, with the reset gate (ØR) clocked normally or held at clock low level.

An external load is required for each output amplifier. For the HR amplifier, this can be a resistor of about 5 k $\Omega$  (non-critical) or a constant current type of about 5 mA. For the LS amplifier, the load should be either 5 k $\Omega$  or 5 mA. The on-chip amplifier power dissipation is approximately 30 mW for the HR amplifier and 40 mW for the LS amplifier.

#### DRIVE PULSE WAVEFORM SPECIFICATION

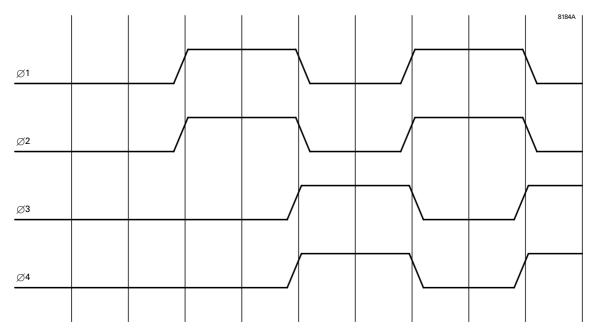

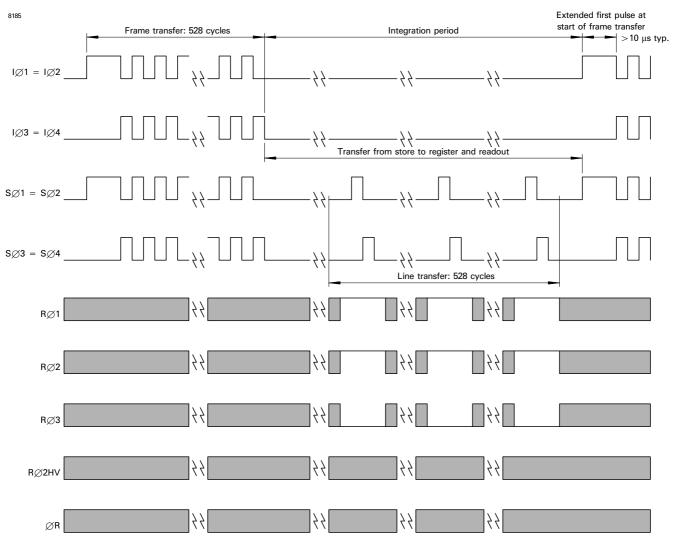

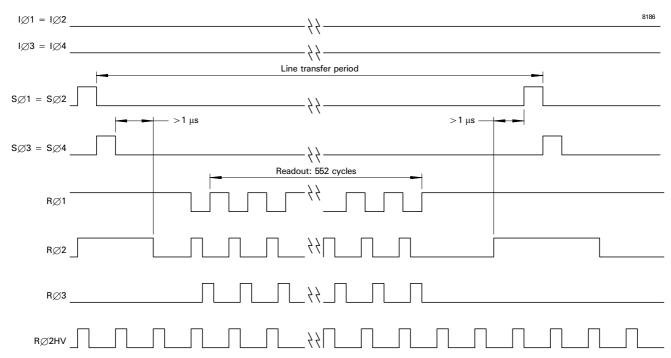

The device is of a 4-phase construction, designed to operate in 2-phase inverted mode. This is achieved by applying common timings to phases  $\emptyset$ 1 and  $\emptyset$ 2, and phases  $\emptyset$ 3 and  $\emptyset$ 4 of the image and store sections. Suggested timing diagrams are shown in Figs. 4 - 11. The following are suggested pulse rise and fall times.

| CLOCK PULSE | TYPICAL RISE TIME $\tau$ (ns) | TYPICAL FALL TIME $\tau$ (ns) | TYPICAL PULSE OVERLAP                                                           |

|-------------|-------------------------------|-------------------------------|---------------------------------------------------------------------------------|

| IØ          | $120 < \tau < 200$            | $120 < \tau < 200$            | @90% points                                                                     |

| SØ          | $120 < \tau < 200$            | $120 < \tau < 200$            | @90% points                                                                     |

| RØ1         | 10                            | 10                            | @70% points                                                                     |

| RØ2         | 10                            | 10                            | @70% points                                                                     |

| RØ3         | 10                            | 10                            | @70% points                                                                     |

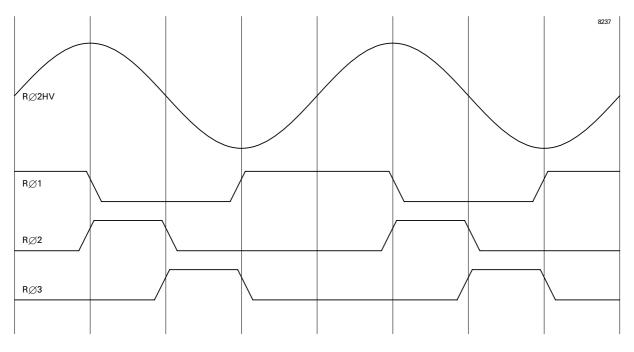

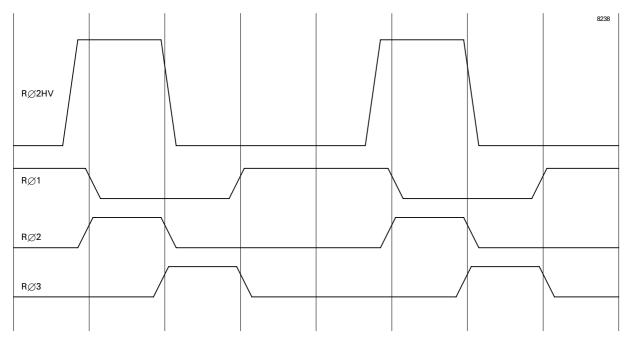

| RØ2HV       | 25                            | 25                            | see note 15                                                                     |

| RØ2HV       | Sine                          | Sine                          | Sinusoid- high on falling edge of $R  ot \! \!                                $ |

#### NOTES

- 14. Register clock pulses are as shown in Figs. 5 and 6.

- 15. An example clocking scheme is shown in Fig. 5. RØ2HV can also be operated with a normal clock pulse, as shown in Fig. 6. The requirement for successful clocking is that RØ2HV reaches its maximum amplitude before RØ1 goes low.

#### **ELECTRICAL INTERFACE CHARACTERISTICS**

| Connection                  | Capacitance to SS | Inter-phase Capacitances       | Total Capacitance | Units |

|-----------------------------|-------------------|--------------------------------|-------------------|-------|

| IØ1                         | 3.7               | 1.6                            | 5.3               | nF    |

| IØ2                         | 1.6               | 1.6                            | 3.2               | nF    |

| IØ3                         | 3.7               | 1.6                            | 5.3               | nF    |

| IØ4                         | 1.6               | 1.6                            | 3.2               | nF    |

| SØ1                         | 3.7               | 1.6                            | 5.3               | nF    |

| SØ2                         | 1.6               | 1.6                            | 3.2               | nF    |

| SØ3                         | 3.7               | 1.6                            | 5.3               | nF    |

| SØ4                         | 1.6               | 1.6                            | 3.2               | nF    |

| RØ1                         | 50                | 65                             | 115               | рF    |

| RØ2                         | 32                | 43                             | 75                | рF    |

| RØ3                         | 62                | 63                             | 125               | рF    |

| RØ2HV                       | 28                | 37                             | 65                | рF    |

| SERIES RESISTANCES          |                   |                                |                   |       |

| Connection                  | Ар                | proximate Total Series Resista | ince              |       |

| IØ1                         |                   | 17                             |                   | Ω     |

| IØ2                         |                   | 17                             |                   | Ω     |

| IØ3                         |                   | 17                             |                   | Ω     |

| IØ4                         |                   | 17                             |                   | Ω     |

| SØ1                         |                   | 17                             |                   | Ω     |

| SØ2                         |                   | 17                             |                   | Ω     |

| SØ3                         |                   | 17                             |                   | Ω     |

| SØ4                         |                   | 17                             |                   | Ω     |

| RØ1                         |                   | 6                              |                   | Ω     |

| RØ2                         |                   | 6                              |                   | Ω     |

| RØ3                         |                   | 6                              |                   | Ω     |

| RØ2HV                       |                   | 2                              |                   | Ω     |

| APPROXIMATE OUTPUT I        | MPEDANCE          |                                |                   |       |

| Large Signal Amplifier      |                   | 350                            |                   | Ω     |

| High Responsivity Amplifier | 250               |                                | Ω                 |       |

Figure 4: CLOCKING SCHEME FOR 2-PHASE INVERTED MODE OPERATION

# Figure 5: CLOCKING SCHEME FOR MULTIPLICATION GAIN (Sine wave clocking scheme) (see note 16)

Figure 6: CLOCKING SCHEME FOR MULTIPLICATION GAIN (Conventional clocking scheme) (see note 16)

#### NOTE

16. To operate through the OSH output amplifier, the RØ1 and RØ2 waveforms should be interchanged.

#### PULSE TIMINGS AND OVERLAPS

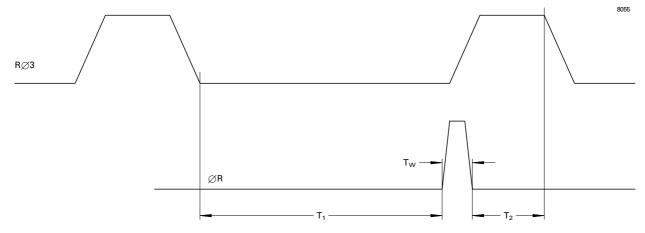

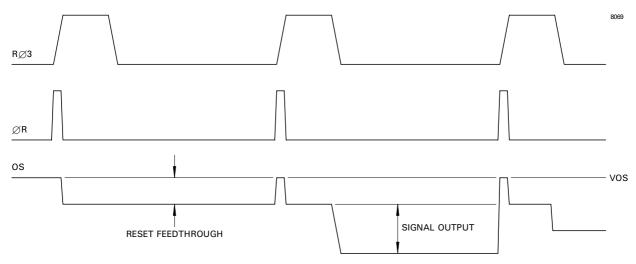

#### Figure 7: RESET PULSE

$T_W = 10 \text{ ns typical}$   $T_1 = \text{output valid}$  $T_2 > 0 \text{ ns}$

#### Figure 8: PULSE AND OUTPUT TIMING

#### Figure 9: EXAMPLE FRAME TIMING DIAGRAM

Figure 10: EXAMPLE LINE TIMING DIAGRAM (Operation through OSL, see notes 16 and 19)

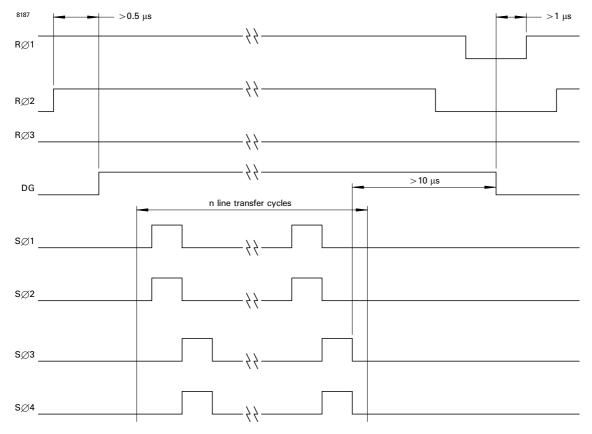

# Figure 11: OPERATION OF THE DUMP GATE TO DUMP n LINES OF UNWANTED DATA FROM THE STANDARD REGISTER

#### NOTE

17. Wanted lines of data must be completely read out before dumping unwanted data.

## Figure 12: OUTPUT CIRCUIT SCHEMATIC (OSL and OSH Amplifiers)

#### NOTE

18. The amplifiers have a DC restoration circuit that is internally activated whenever  $S\emptyset4$  is high.

## Figure 13: SCHEMATIC CHIP DIAGRAM

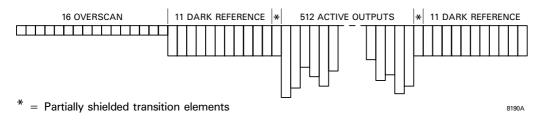

#### Figure 14: LINE OUTPUT FORMAT (for Example Line Timing Figure 10)

#### NOTE

19. There is a 1-line propagation delay between transferring a line from the store section to the standard register and reading it out through the OSL output amplifier.

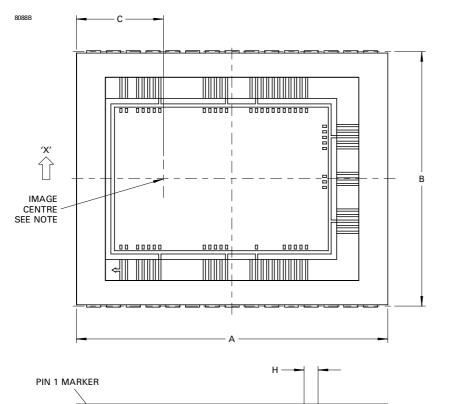

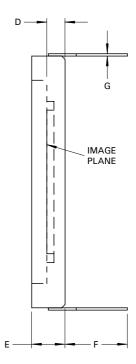

#### Figure 15: PACKAGE OUTLINE (All dimensions without limits are nominal)

L PITCH

| Ref | Millimetres                |  |

|-----|----------------------------|--|

| A   | 28.0 ± 0.28                |  |

| В   | 22.86 ± 0.25               |  |

| С   | 7.83 ± 0.25                |  |

| D   | 1.68 ± 0.25                |  |

| E   | $3.0 \pm 0.3$              |  |

| F   | 5.6                        |  |

| G   | $0.250 + 0.051 \\ - 0.025$ |  |

| Н   | 0.889                      |  |

| J   | 1.270 ± 0.254              |  |

| К   | 0.457 ± 0.051              |  |

| L   | 1.778 ± 0.130              |  |

## Outline Note

The image centre is aligned centrally in the package in direction 'X', to within a tolerance of  $\pm 0.2$  mm.

Whilst e2v technologies has taken care to ensure the accuracy of the information contained herein it accepts no responsibility for the consequences of any use thereof and also reserves the right to change the specification of goods without notice. e2v technologies accepts no liability beyond that set out in its standard conditions of sale in respect of infringement of third party patents arising from the use of tubes or other devices in accordance with information contained herein.