# CCD230-42 Front Illuminated Scientific CCD Sensor 2048 x 2048 Pixels, Four Outputs and Inverted Mode Operation

### INTRODUCTION

This device extends e2v's family of scientific CCD sensors. The CCD230 has been designed to provide a large image area for demanding scientific imaging applications. The low readout noise/high speed amplifier gives exceptional sensitivity with minimum readout times and the inverted mode of operation gives lowest dark current.

### DESCRIPTION

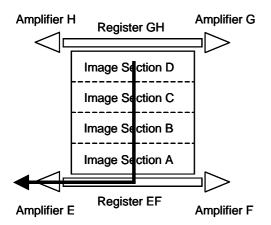

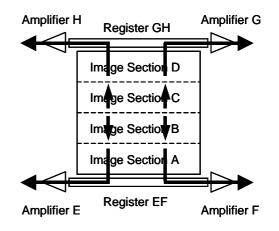

The sensor has an image area having 2048 x 2064 pixels, split readout registers at both top and bottom with charge detection amplifiers at both ends. The pixel size is 15  $\mu$ m square. The image area has four separately connected sections to allow full-frame, frame transfer, split full frame or split frame-transfer modes. Depending on the mode, the readout can be through 1, 2 or 4 of the output circuits. A gate-controlled drain is also provided to allow fast dumping of unwanted data.

The output amplifier is a two-stage type designed to give minimum noise at pixel rates as high as 5 MHz. The low output impedance of 400  $\Omega$  simplifies the interface with external electronics. Dummy outputs are also available to facilitate common mode rejection.

To achieve maximum full-well capacity, a four-phase image clocking sequence should be used. The detailed clock sequences are given in this data sheet.

The readout register is designed to accommodate at least four image pixels of charge, but the maximum signal then exceeds the capacity of the output circuit unless the output is operated in low responsivity mode.

Specifications are guaranteed and tested at -25 °C.

## **OTHER VARIANTS**

The CCD230-42 is available with a 3 mm fibre-optic stud.

Back-illuminated and NIMO versions of the basic CCD230 are also available. Devices with other formats (up to 8192 x 3172 pixels) can also be provided. A variant is also available with an alternative very low noise amplifier but with lower charge handling capacity (CCD231).

Consult e2v technologies for further information.

### SUMMARY SPECIFICATION

| Number of pixels               | 2048(H) x 2064(V)                                       |

|--------------------------------|---------------------------------------------------------|

| Pixel size                     | 15 µm square                                            |

| Image area                     | 30.7 mm x 30.7 mm                                       |

| Outputs                        | 4                                                       |

| Package size                   | 42.0 x 61.0 mm                                          |

| Package format                 | alumina PGA                                             |

| Focal plane height, above base | 2.75 mm                                                 |

| Connectors                     | Pin Grid Array (PGA)                                    |

| Flatness                       | <20 µm (peak to valley)                                 |

| Amplifier sensitivity          | 2.7 µV/e⁻                                               |

| Readout noise                  | 8 e <sup>−</sup> at 1 MHz<br>3 e <sup>−</sup> at 50 kHz |

| Maximum data rate              | 5 MHz                                                   |

| Charge storage                 | 150,000 e <sup>−</sup>                                  |

| Dark signal                    | 0.1 e <sup>-</sup> /pixel/second<br>(at –25 °C)         |

Quoted performance parameters given here are "typical" values. Specification limits are shown later in this data sheet.

#### **Part References**

CCD230-42-g-xxx g = cosmetic grade 144 = specific part number for the IMO FI CCD230-42

e2v technologies (uk) limited, Waterhouse Lane, Chelmsford, Essex CM1 2QU United Kingdom Holding Company: e2v technologies plc

Telephone: +44 (0)1245 493493 Facsimile: +44 (0)1245 492492

Contact e2v by e-mail: <u>enquiries@e2v.com</u> or visit <u>www.e2v.com</u> for global sales and operations centres.

Whilst e2v technologies has taken care to ensure the accuracy of the information contained herein it accepts no responsibility for the consequences of any use thereof and also reserves the right to change the specification of goods without notice. e2v technologies accepts no liability beyond the set out in its standard conditions of sale in respect of infringement of third party patents arising from the use of tubes or other devices in accordance with information contained herein.

## PERFORMANCE (At 223 K unless stated)

### **Electro-Optical Specification**

|                                                              | Min                | Typical            | Max        | Units                   | Note |

|--------------------------------------------------------------|--------------------|--------------------|------------|-------------------------|------|

| Peak charge storage (image)                                  | 120,000            | 150,000            | -          | e <sup>-</sup> /pixel   | 2    |

| Peak charge storage (register)                               | -                  | 850,000            | -          | e <sup>-</sup> /pixel   | 2    |

| Output node capacity:<br>OG low (mode 1)<br>OG high (mode 2) | -                  | 450,000<br>900,000 | -          | e⁻<br>e⁻                | 3    |

| Output amplifier responsivity:<br>mode 1<br>mode 2           | 1.8<br>-           | 2.7<br>0.8         | -          | μV/e⁻<br>μV/e⁻          | 3    |

| Readout noise                                                | -                  | 7                  | 12         | e⁻ rms                  | 4    |

| Readout frequency                                            | -                  | 1000               | 5000       | kHz                     | 5    |

| Dark signal (at 248 K)                                       | -                  | 0.1                | 1.0        | e <sup>-</sup> /pixel/s | 6    |

| Charge transfer efficiency:<br>parallel<br>serial            | 99.9990<br>99.9990 | 99.9995<br>99.9995 | 100<br>100 | %<br>%                  | 7    |

| Spectral range                                               | 420                | -                  | 1060       | nm                      |      |

### NOTES

- 1. Device performance will be within the limits specified by "max" and "min" when operated at the recommended voltages supplied with the test data and when measured at a register clock frequency of approximately 0.5 1.0 MHz. The noise as specified is separately measured in accordance with note 4.

- 2. Signal level at which resolution begins to degrade.

- 3. Under normal operation (mode 1), SW is operated as a summing well or clocked as RØ3. OG is biased at typically 2 V. Alternatively, SW may be operated as a second output gate (and not therefore available for summing), biased at typically 2 V with OG raised to a high voltage (mode 2) to give more charge handling capacity (e.g. for higher level pixel binning). With OG high, the output noise will also increase by a factor of two.

- 4. Measured with correlated double sampling at 750 kHz pixel rate.

- 5. Depending on the external load capacitance to be driven. The register will transfer charge at higher frequencies, but performance cannot be guaranteed.

- Dark signal is typically measured with the substrate voltage at +9 V with respect to image clock low and the device temperature 248 K. It is a strong function of temperature and the typical average (background) dark signal at any temperature T (kelvin) between 248 K and 300 K is given by:

$Q_d/Q_{do} = 1.4 \times 10^6 T^3 e^{-9080/T}$

where  $Q_{\text{do}}\,\text{is}$  the dark current at 293 K.

Transfer through the image sections can give rise to an additional temperature-independent component of "clock-induced charge" with of a magnitude in the region of  $10^{-4}$  electrons per pixel transfer.

7. Measured with either a 55Fe X-ray source or an optical illumination to approximately 3,000 e<sup>-</sup>/pixel. The CTE value is quoted for the complete clock cycle (i.e. all phases).

# **COSMETIC SPECIFICATIONS**

Maximum allowed defect levels are indicated below.

| Grade                          | 0   | 1   | 2   |

|--------------------------------|-----|-----|-----|

| Column defects, black or white | 0   | 1   | 4   |

| White spots                    | 50  | 75  | 100 |

| Total (black & white) spots    | 100 | 150 | 200 |

| Traps > 200e-                  | 10  | 20  | 30  |

**Grade 5** devices are fully functional but with an image quality below that of grade 2, and may not meet all other specifications. Not all parameters may be tested.

## DEFINITIONS

| White spots           | A defect is counted as a white spot if the dark generation rate is $\ge 250 \text{ e}^-\text{/pixel/s}$ at 248 K.<br>The typical temperature dependence is given by $Q_d/Q_{do} = 122T^3 e^{-6400/T}$ |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Black spots           | A black spot defect is a pixel with a response less than 90% of the local mean signal.                                                                                                                |

| Column defects        | A column is counted as a defect if it contains at least 50 white or dark single pixel defects.                                                                                                        |

| Traps                 | A trap causes charge to be temporarily held in a pixel and these are counted as defects if the quantity of trapped charge is greater than 200 e <sup>-</sup>                                          |

| Defect exclusion zone | Defect measurements are excluded from the outer two rows and columns of the sensor.                                                                                                                   |

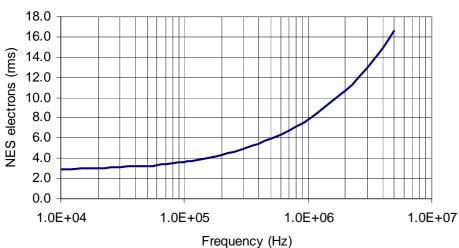

# **TYPICAL OUTPUT AMPLIFIER NOISE**

The variation of typical read noise with operating frequency is shown below. (Measured using correlated double sampling with a pre-sampling bandwidth equal to twice the pixel rate in mode 1 at approximately 248 K).

### Estimated Read Noise (FI)

### DEFINITIONS

#### Inverted Mode (IMO)

An inverted mode CCD has an additional implant that allows charge integration to be carried out with all clock phases low. With a high voltage applied to the substrate (typically +9 V) this causes the whole of the device to be flooded with holes (inverted or pinned), which suppresses the surface component of dark signal. This leaves only the much lower bulk component, reducing the overall dark signal by a factor of approximately 100.

Inverted mode operation is also referred to as multi-phase pinning (MPP).

#### **Readout Noise**

Readout noise is the random noise from the CCD output stage in the absence of signal. This noise introduces a random fluctuation in the output voltage that is superimposed on the detected signal.

The method of measurement involves reverse-clocking the register and determining the standard deviation of the output fluctuations, and then converting the result to an equivalent number of electrons using the known amplifier responsivity.

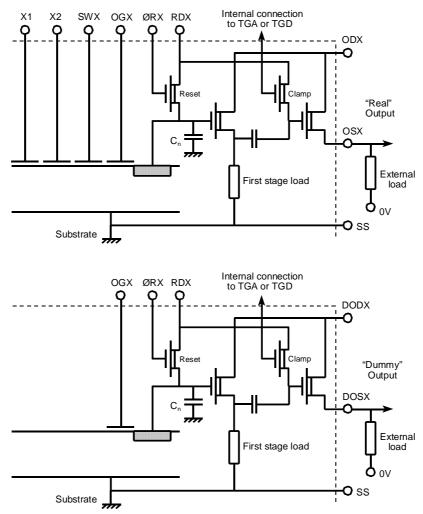

#### **Dummy Output**

Each output has an associated "dummy" circuit on-chip, which is of identical design to the "real" circuit but receives no signal charge. The dummy output should have the same levels of clock feed-through, and can thus be used to suppress the similar component in the "real" signal output by means of a differential pre-amplifier. The penalty is that the noise is increased by a factor of  $\sqrt{2}$ . If not required the dummy outputs may be powered down.

#### Dark Signal

This is the output signal of the device with zero illumination. This typically consists of thermally generated electrons within the semiconductor material, which are accumulated during signal integration. Dark signal is a strong function of temperature as described in note 6.

#### **Correlated Double Sampling**

A technique for reducing the noise associated with the charge detection process by subtracting a first output sample taken just after reset from a second sample taken with charge present.

#### **Charge Transfer Efficiency**

The fraction of charge stored in a CCD element that is transferred to the adjacent element by a single clock cycle. The charge not transferred remains in the original element, possibly in trapping states and may possibly be released into later elements. The value of CTE is not constant but varies with signal size, temperature and clock frequency.

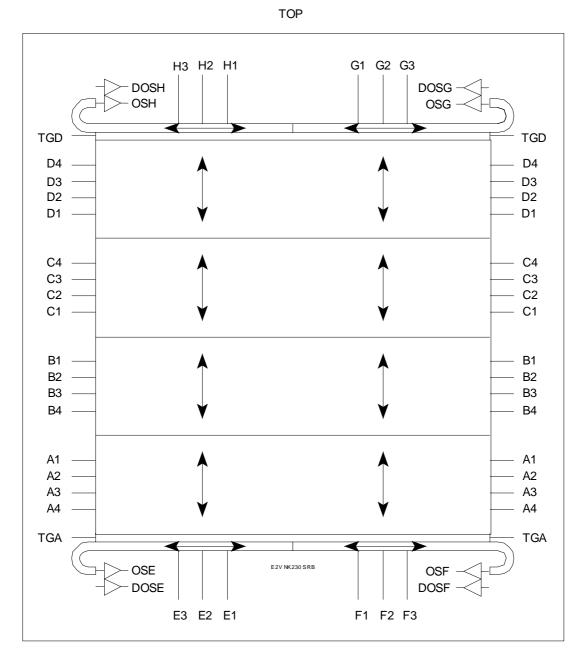

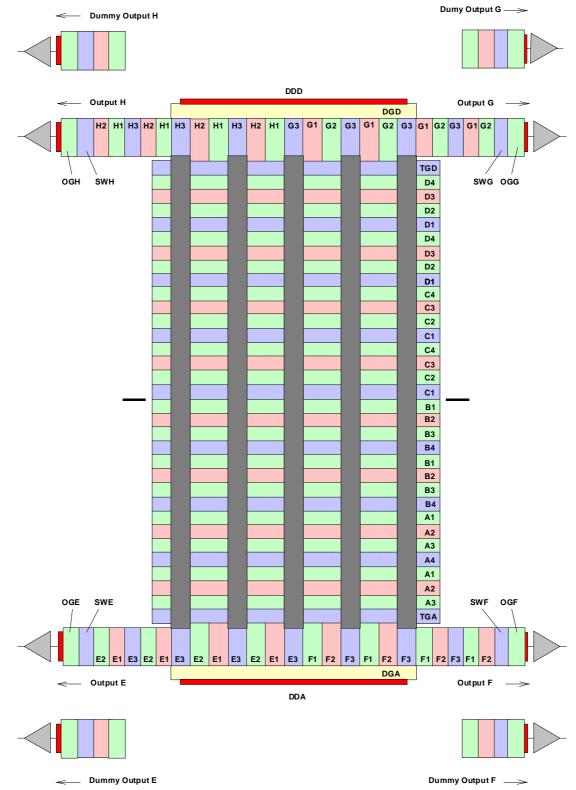

# ARCHITECTURE

## **Chip Schematic**

BOTTOM

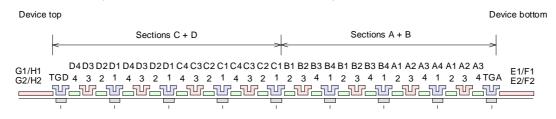

## **ARRANGEMENT OF ELECTRODES**

The IMO implant is under image phases A4, B4, C1, D1 and the transfer gates as shown below.

# **OUTPUT CIRCUIT**

X designates a specific output, namely E, F, G or H

The first stage load of each output (real or dummy) draws a quiescent current of approximately 0.3 mA.

The output circuit consists of two capacitor-coupled source-follower stages. This particular design has a reduced responsivity to allow binning of large charge packets. The load for the first stage is on-chip and that for the second stage is external, as next described. The DC restoration circuitry requires a pulse at the start of line readout, and this is automatically obtained by an internal connection to the adjacent transfer gate, TG. Transferring a line of charges to the register thus automatically activates the circuitry. N.B. TG pulses still need to be applied at similar intervals if only the register and/or output circuit are being operated, e.g. for test or characterisation purposes.

If an output is to be powered down, it is recommended that either OD or DOD be set to SS voltage, taking care that the maximum ratings are never exceeded or that OD and DOD be disconnected. If external loads return to a voltage below SS they should also be disconnected.

# ELECTRICAL INTERFACE

# CONNECTIONS, TYPICAL VOLTAGES AND ABSOLUTE MAXIMUM RATINGS

The tables below give the pin-outs and clock amplitudes. Note that the hyphenated suffix symbols (e.g.  $\emptyset$ R-H) indicate to which amplifier the CCD pin relates.

|     |        |                                  |     | MPLITUDE OR<br>(V) (see note 10 |      | MAX RATINGS<br>with respect to |

|-----|--------|----------------------------------|-----|---------------------------------|------|--------------------------------|

| PIN | REF    | DESCRIPTION                      | Min | Typical                         | Max  | V <sub>SS</sub> (V)            |

| 1   | B2     | Image Area Clock Phase 2 (B)     | 9   | 11                              | 12   | ±20                            |

| 2   | B1     | Image Area Clock Phase 1 (B)     | 9   | 11                              | 12   | ±20                            |

| 3   | B3     | Image Area Clock Phase 3 (B)     | 9   | 11                              | 12   | ±20                            |

| 4   | B4     | Image Area Clock Phase 4 (B)     | 9   | 11                              | 12   | ±20                            |

| 5   | DOD-E  | Dummy Output Drain (E)           | 27  | 30                              | 31   | -0.3 to +35                    |

| 6   | TG-A   | Transfer Gate (A)                | 9   | 11                              | 12   | ±20                            |

| 7   | ØR-E   | Reset Gate (E)                   | 9   | 11                              | 12   | ±20                            |

| 8   | RD-E   | Reset Drain (E)                  | 16  | 18                              | 19   | -0.3 to +25                    |

| 9   | DOS-E  | Dummy Output Source (E)          |     | See note 8                      |      | N/A                            |

| 10  | SS     | Substrate                        | 8   | 9                               | 10.5 | N/A                            |

| 11  | OD-E   | Output Drain (E)                 | 27  | 30                              | 31   | -0.3 to +35                    |

| 12  | OS-E   | Output Source (E)                |     | See note 8                      |      | N/A                            |

| 13  | SS     | Substrate                        | 8   | 9                               | 10.5 | N/A                            |

| 14  | OG-E   | Output Gate (E) (see note 9)     | 1   | 3                               | 5    | ±20                            |

| 15  | N/C    | No Connection                    |     | -                               |      | N/A                            |

| 16  | E2     | Register Clock Phase 2 (E)       | 9   | 11                              | 12   | ±20                            |

| 17  | E1     | Register Clock Phase 1 (E)       | 9   | 11                              | 12   | ±20                            |

| 18  | SWØ-E  | Summing Well (E) (see note 9)    | 9   | 11                              | 12   | ±20                            |

| 19  | DG-A   | Dump Gate (A) (see note 11)      | -2  | 0                               | 0.5  | ±20                            |

| 20  | DD-A   | Dump Drain (A)                   | 27  | 30                              | 31   | -0.3 to +35                    |

| 21  | E3, F3 | Register Clock Phase 3 (F and E) | 9   | 11                              | 12   | ±20                            |

| 22  | F1     | Register Clock Phase 1 (F)       | 9   | 11                              | 12   | ±20                            |

| 23  | F2     | Register Clock Phase 2 (F)       | 9   | 11                              | 12   | ±20                            |

| 24  | SWØ-F  | Summing Well (F) (see note 9)    | 9   | 11                              | 12   | ±20                            |

| 25  | SS     | Substrate                        | 8   | 9                               | 10.5 | N/A                            |

| 26  | OG-F   | Output Gate (F) (see note 9)     | 1   | 3                               | 5    | ±20                            |

| 27  | N/C    | No Connection                    |     | -                               |      | N/A                            |

| 28  | SS     | Substrate                        | 8   | 9                               | 10.5 | N/A                            |

| 29  | OD-F   | Output Drain (F)                 | 27  | 30                              | 31   | -0.3 to +35                    |

| 30  | OS-F   | Output Source (F)                |     | See note 8                      |      | N/A                            |

| 31  | ØR-F   | Reset Gate (F)                   | 9   | 11                              | 12   | ±20                            |

| 32  | RD-F   | Reset Drain (F)                  | 16  | 18                              | 19   | -0.3 to +25                    |

| 33  | DOS-F  | Dummy Output Source (F)          |     | See note 8                      |      | N/A                            |

| 34  | A4     | Image Area Clock Phase 4 (A)     | 9   | 11                              | 12   | ±20                            |

| 35  | DOD-F  | Dummy Output Drain (F)           | 27  | 30                              | 31   | -0.3 to +35                    |

| 36  | TG-A   | Transfer Gate (A)                | 9   | 11                              | 12   | ±20                            |

| 37  | A2     | Image Area Clock Phase 2 (A)     | 9   | 11                              | 12   | ±20                            |

| 38  | A1     | Image Area Clock Phase 1 (A)     | 9   | 11                              | 12   | ±20                            |

| 39  | A3     | Image Area Clock Phase 3 (A)     | 9   | 11                              | 12   | ±20                            |

|     |        |                                  | CLOCK | AMPLITUDE OR<br>(V) (see note 10 | MAX RATINGS<br>with respect to |                     |

|-----|--------|----------------------------------|-------|----------------------------------|--------------------------------|---------------------|

| PIN | REF    | DESCRIPTION                      | Min   | Typical                          | Max                            | V <sub>SS</sub> (V) |

| 40  | C3     | Image Area Clock Phase 3 (C)     | 9     | 11                               | 12                             | ±20                 |

| 41  | C4     | Image Area Clock Phase 4 (C)     | 9     | 11                               | 12                             | ±20                 |

| 42  | C2     | Image Area Clock Phase 2 (C)     | 9     | 11                               | 12                             | ±20                 |

| 43  | C1     | Image Area Clock Phase 1 (C)     | 9     | 11                               | 12                             | ±20                 |

| 44  | DOD-G  | Dummy Output Drain (G)           | 27    | 30                               | 31                             | -0.3 to +35         |

| 45  | TG-D   | Transfer Gate (D)                | 9     | 11                               | 12                             | ±20                 |

| 46  | ØR-G   | Reset Gate (G)                   | 9     | 11                               | 12                             | ±20                 |

| 47  | RD-G   | Reset Drain (G)                  | 16    | 18                               | 19                             | -0.3 to +25         |

| 48  | DOS-G  | Dummy Output Source (G)          |       | See note 8                       |                                | N/A                 |

| 49  | SS     | Substrate                        | 8     | 9                                | 10.5                           | N/A                 |

| 50  | OD-G   | Output Drain (G)                 | 27    | 30                               | 31                             | -0.3 to +35         |

| 51  | OS-G   | Output Source (G)                |       | See note 8                       |                                | N/A                 |

| 52  | SS     | Substrate                        | 8     | 9                                | 10.5                           | N/A                 |

| 53  | OG-G   | Output Gate (G) (see note 9)     | 1     | 3                                | 5                              | ±20                 |

| 54  | N/C    | No Connection                    |       | -                                |                                | N/A                 |

| 55  | G2     | Register Clock Phase 2 (G)       | 9     | 11                               | 12                             | ±20                 |

| 56  | G1     | Register Clock Phase 1 (G)       | 9     | 11                               | 12                             | ±20                 |

| 57  | SWØ-G  | Summing Well (G) (see note 9)    | 9     | 11                               | 12                             | ±20                 |

| 58  | DG-D   | Dump Gate (D) (see note 11)      | -2    | 0                                | 0.5                            | ±20                 |

| 59  | DD-D   | Dump Drain (D)                   | 27    | 30                               | 31                             | -0.3 to +35         |

| 60  | G3, H3 | Register Clock Phase 3 (G and H) | 9     | 11                               | 12                             | ±20                 |

| 61  | H1     | Register Clock Phase 1 (H)       | 9     | 11                               | 12                             | ±20                 |

| 62  | H2     | Register Clock Phase 2 (H)       | 9     | 11                               | 12                             | ±20                 |

| 63  | SWØ-H  | Summing Well (H) (see 0)         | 9     | 11                               | 12                             | ±20                 |

| 64  | SS     | Substrate                        | 8     | 9                                | 10.5                           | N/A                 |

| 65  | OG-H   | Output Gate (H) (see 0)          | 1     | 3                                | 5                              | ±20                 |

| 66  | N/C    | No Connection                    |       | -                                |                                | N/A                 |

| 67  | SS     | Substrate                        | 8     | 9                                | 10.5                           | N/A                 |

| 68  | OD-H   | Output Drain (H)                 | 27    | 30                               | 31                             | -0.3 to +35         |

| 69  | OS-H   | Output Source (H)                |       | See note 8                       |                                | N/A                 |

| 70  | ØR-H   | Reset Gate (H)                   | 9     | 11                               | 12                             | ±20                 |

| 71  | RD-H   | Reset Drain (H)                  | 16    | 18                               | 19                             | -0.3 to +25         |

| 72  | DOS-H  | Dummy Output Source (H)          |       | See note 8                       |                                | N/A                 |

| 73  | D1     | Image Area Clock Phase 1 (D)     | 9     | 11                               | 12                             | ±20                 |

| 74  | DOD-H  | Dummy Output Drain (H)           | 27    | 30                               | 31                             | -0.3 to +35         |

| 75  | TG-D   | Transfer Gate (D)                | 9     | 11                               | 12                             | ±20                 |

| 76  | D3     | Image Area Clock Phase 3 (D)     | 9     | 11                               | 12                             | ±20                 |

| 77  | D4     | Image Area Clock Phase 4 (D)     | 9     | 11                               | 12                             | ±20                 |

| 78  | D2     | Image Area Clock Phase 2 (D)     | 9     | 11                               | 12                             | ±20                 |

## See Notes Overleaf

#### NOTES

Do not connect to voltage supply but use a ~5 mA current source or a ~5 kΩ external load. The quiescent voltage on OS is then about 6 - 8 V above the reset drain voltage and is typically 24 V. The current through these pins must not exceed 20 mA. Permanent damage may result if, in operation, OS or DOS experience short circuit conditions.

For highest speed operation the output load resistor can be reduced from 5 k $\Omega$  to approximately 2.2 k $\Omega$ , but note that this will increase power consumption. If the device is to be operated with a register clock period of below about 1 MHz then the load may be increased to 10 k $\Omega$  to reduce power consumption.

In order to ensure that the amplifier is well settled the output load capacitance should be minimised (typically <20 pF) for the highest readout rate.

9. Default operation (mode 1) shown with OG at +2 V typical. In this mode SW may be clocked as RØ3 if a summing well function is not required.

For alternative operation in a low responsivity mode with increased charge handling, OG should be set to +20 V and SW should be operated as OG. Charge is now read out as  $R\emptyset 2$  goes low.

10. To ensure that any device can be operated the camera should be designed so that any value in the range "min" to "max" can be provided. All operating voltages are with respect to image clock low (nominally 0 V).

The clock pulse low levels should be in the range  $0 \pm 0.5$  V for image, register, SW and DG clocks.

- 11. Non-charge dumping level shown. For charge dumping, DG should be pulsed to 12 ± 2 V (this may be provided from a common rail to the register clocks).

- 12. This data sheet assumes that all signals are relative to the clock low level of 0 V. The absolute level for all biases and clock rails may be changed to suit the needs of the designer provided the relative levels are maintained. For example, it is acceptable to set Vss to 0 V so long as the specified difference between Vss and all other bias and clock voltages is maintained and the current load on all output sources is as recommended in note 8.

- 13. DD and OD may be provided from a common rail provided that they are separately filtered sufficiently to ensure that there is no clock pick-up on OD.

- 14. Image and register clock high voltages may be provided from common rails.

# **ELECTRICAL INTERFACE CHARACTERISTICS**

### Electrode capacitances (defined at mid-clock level)

|                                                        | Typical | Units |

|--------------------------------------------------------|---------|-------|

| IØ/IØ inter-phase [A, B, C and D]                      | 2.5     | nF    |

| IØ/SS [A1, A2, A3, B1, B2, B3, C2, C3, C4, D2, D3, D4) | 5       | nF    |

| IØ/SS [4-A, 4-B, 1-C, 1-D]                             | 12      | nF    |

| Transfer gates [TGA, TGD]                              | 65      | pF    |

| RØ/(SS + DG + DD) [E1, F1, G1, H1]                     | 95      | pF    |

| RØ/(SS + DG + DD) [E2, F2, G2, H2]                     | 90      | pF    |

| RØ/(SS + DG + DD) [E3, F3, G3, H3]                     | 80      | pF    |

The total capacitance on each phase is the sum of the inter-phase capacitance to each of the adjacent phases and the capacitance of the phase to substrate. For example, the total capacitance on phase A1 is 2 times 2.5 nF plus 5 nF for a total of 10 nF.

The amplifier output impedance is typically 400  $\Omega$ .

## POWER UP/POWER DOWN

When powering the device up or down it is critical that any specified maximum rating is not exceeded. Specifically the voltage for the amplifier and dump drains (pins 5, 8, 11, 20, 29, 32, 35, 44, 47, 50, 59, 68, 71 and 74) must never be taken negative with respect to the substrate. Hence, if the substrate is to be operated at a positive voltage (e.g. to minimise dark current) then the drive electronics should have a switch-on sequence which powers up all the drains to their positive voltages before the substrate voltage starts to increase from zero.

It is also important to ensure that excess currents (see note 8) do not flow in the OS or DOS pins. Such currents could arise from rapid charging of a signal coupling capacitor or from an incorrectly biased DC-coupled preamplifier.

Similarly, for powering down, the substrate must be taken to zero voltage before the drains.

## POWER CONSUMPTION

The power dissipated within the CCD is a combination of the static dissipation of the amplifiers and the dynamic dissipation from the parallel and serial clocking (i.e. driving the capacitive loads).

The table below gives representative values for the components of the on-chip power dissipation for the case of continuous split-frame line-by-line read-out using both registers and all the output circuits with both real and dummy amplifiers activated. The frequency is that for clocking the serial register and an appropriate value of the amplifier load is utilised in each case.

| Readout   |           | Amplifier | Power dissipation |                          |       |          |  |

|-----------|-----------|-----------|-------------------|--------------------------|-------|----------|--|

| frequency | Line time | load      | Amplifiers        | Amplifiers Serial clocks |       | Total    |  |

| 100 kHz   | 11 ms     | 10 kΩ     | 165 mW            | 9 mW                     | 2 mW  | 176 mW   |  |

| 1 MHz     | 1.1 ms    | 5 kΩ      | 275 mW            | 85 mW                    | 17 mW | 377 mW   |  |

| 5 MHz     | 250 µs    | 2.2 kΩ    | 525 mW            | 425 mW                   | 75 mW | 1,025 mW |  |

The dissipation reduces to only that of the amplifiers during the time that charge is being collected in the image sections with both the parallel and serial clocks static.

## FRAME READOUT MODES

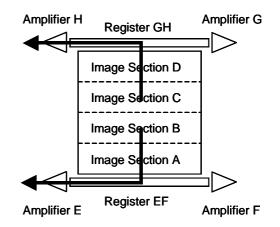

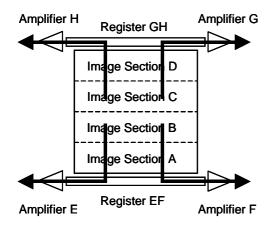

The device can be operated in a full-frame or frame transfer mode with readout from one, two or four amplifiers. These modes are determined by the clock pulse sequences applied to the image and register clocks. The diagrams below show some of the transfer options that are possible.

Full frame read-out through one amplifier

Split full frame read-out through two amplifiers

Split full frame read-out through four amplifiers

Split frame transfer through four amplifiers

If the applied drive pulses are designated  $I \varnothing 1$ ,  $I \varnothing 2$ ,  $I \varnothing 3$  and  $I \varnothing 4$ , then connections should be made as tabulated below to effect the following directions of transfer.

|                                         | IØ1 | IØ2 | IØ3 | IØ4 |             |

|-----------------------------------------|-----|-----|-----|-----|-------------|

| A section transfer towards E-F register | A4  | A1  | A2  | A3  | TGA = I∅1   |

| B section transfer towards E-F register | B4  | B1  | B2  | B3  |             |

| C section transfer towards G-H register | C1  | C2  | C3  | C4  |             |

| D section transfer towards G-H register | D1  | D2  | D3  | D4  | TGD = I∅1   |

| A section transfer towards G-H register | A4  | A3  | A2  | A1  | TGA = "low" |

| B section transfer towards G-H register | B4  | B3  | B2  | B1  |             |

| C section transfer towards E-F register | C1  | C4  | C3  | C2  |             |

| D section transfer towards E-F register | D1  | D4  | D3  | D2  | TGD = "low" |

The first four transfer sequences are for split full-frame readout. The second four are for reversing the transfer direction in either section for readout to only one of the registers.

Transfer from the image section to the register is into the phase 1 and 2 electrodes, i.e. E1, F1, G1, H1, E2, F2, G2 and H2. These electrodes must be held at clock "high" level during the process. If the register pulses are designated R $\emptyset$ 1, R $\emptyset$ 2 and R $\emptyset$ 3, then connections should be made as tabulated below to effect the following directions of transfer.

| Clock Generator Drive Pulse Name    | RØ1 | RØ2 | RØ3 |

|-------------------------------------|-----|-----|-----|

|                                     | RØT |     |     |

| E section transfer towards E output | E1  | E2  | E3  |

| F section transfer towards F output | F1  | F2  | F3  |

| G section transfer towards G output | G1  | G2  | G3  |

| H section transfer towards H output | H1  | H2  | H3  |

| E section transfer towards F output | E2  | E1  | E3  |

| F section transfer towards E output | F2  | F1  | F3  |

| G section transfer towards H output | G2  | G1  | G3  |

| H section transfer towards G output | H2  | H1  | H3  |

The first four sequences are for split register readout to all four outputs. The second four are for the reversal of direction in any half-section.

The last electrode before the output gate is separately connected to give the function of a summing well (SW). In normal readout (i.e. if not used for summing), SW is clocked as  $R\emptyset$ 3. For summing, the selected SW gate is held at clock "high" level for the required number of readout cycles, and then clocked as  $R\emptyset$ 3 to output charge.

Alternatively, SW may be operated as a second output gate to provide the option of operation in low gain/high signal mode (mode 2) with OG high. If this mode of operation is used, then the sequencing of the output clocks must be changed, as charge will be transferred into the output node as  $R \varnothing 2$  goes low (see note 9).

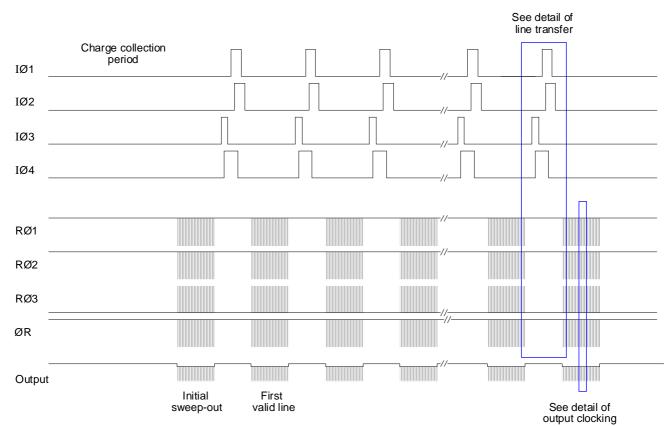

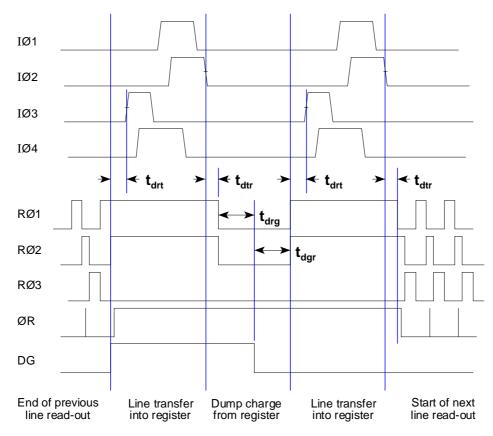

# FRAME READOUT TIMING DIAGRAM

# DETAIL OF LINE TRANSFER

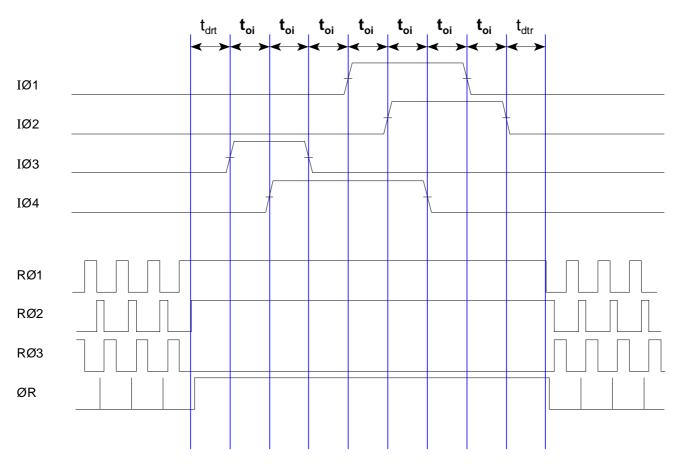

# DETAIL OF OUTPUT CLOCKING (with SW clocked as RØ3)

## DETAIL OF VERTICAL LINE TRANSFER (Single line dump)

# **CLOCK TIMING REQUIREMENTS**

| Symbol           | Description                                                    | Minimum            | Typical | Maximum             | Units |

|------------------|----------------------------------------------------------------|--------------------|---------|---------------------|-------|

| Ti               | Line transfer time (see note 15)                               | 45                 | 72      | (see note 17)       | μs    |

| t <sub>oi</sub>  | Image clock pulse edge overlap                                 | 5                  | 8       | (see note 17)       | μs    |

| t <sub>ri</sub>  | Image clock and transfer gate pulse rise time                  | 0.5                | 1       | 0.3 t <sub>oi</sub> | μs    |

| t <sub>fi</sub>  | Image clock pulse fall time                                    | 0.5                | 1       | 0.3 t <sub>oi</sub> | μs    |

| t <sub>drt</sub> | Delay time, RØ stop to IØ rising                               | 5                  | 85      | (see note 17)       | μS    |

| t <sub>dtr</sub> | Delay time, IØ falling to RØ start                             | 5                  | 8       | (see note 17)       | μs    |

| T <sub>rr</sub>  | Register clock period (see note 18)                            | 200                | 1333    | (see note 17)       | ns    |

| t <sub>drg</sub> | Delay time, $R \varnothing$ falling to DG rising (see note 19) | 5                  | 20      | N/A                 | μS    |

| t <sub>dgr</sub> | Delay time, DG falling to $R\emptyset$ rising (see note 19)    | 5                  | 20      | N/A                 | μS    |

| t <sub>rr</sub>  | Register clock pulse rise time                                 | 10                 | 50      | (see note 17)       | ns    |

| T <sub>fr</sub>  | Register clock pulse fall time                                 | 10                 | 50      | (see note 17)       | ns    |

| t <sub>or</sub>  | Register clock pulse edge overlap                              | 10                 | 60      | (see note 17)       | ns    |

| t <sub>wx</sub>  | Reset pulse width (see note 18)                                | >2 t <sub>rx</sub> | 125     | (see note 17)       | ns    |

| t <sub>rx</sub>  | Reset pulse rise time                                          | 2                  | 50      | 0.5 t <sub>WX</sub> | ns    |

| t <sub>fx</sub>  | Reset pulse fall time                                          | 2                  | 50      | 0.5 t <sub>WX</sub> | ns    |

## NOTES

15. Generally  $T_i = t_{drt} + 7t_{oi} + t_{dtr}$ .

- 16. The RØ2 pulse-width is normally minimised, as shown, such that the RØ1 and RØ3 pulse widths can be increased to maximise the output reset (or reference) and signal sampling intervals.

- 17.As set by any system specifications.

- 18. The typical timing is for read-out at frequencies in the region of 750 kHz as per factory testing. Minimum period is that required for operation at 5 MHz but this is untested in the factory.

- 19. Dump gate not used in clocked mode for factory testing. Minimum and typical values are for guide only.

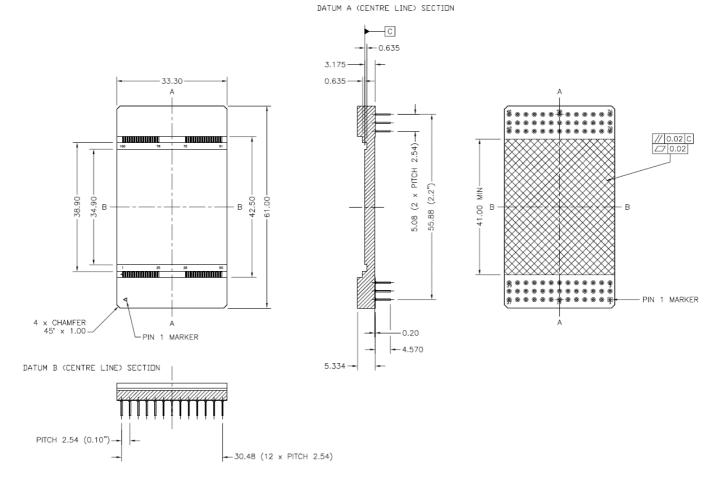

## PACKAGE DETAIL

# HANDLING CCD SENSORS

CCD sensors, in common with most high performance MOS IC devices, are static sensitive. In certain cases, a discharge of static electricity may destroy or irreversibly degrade the device. Accordingly, full antistatic handling precautions should be taken whenever using a CCD sensor or module. These include:

- Working at a fully grounded workbench

- Operator wearing a grounded wrist strap

- All receiving sockets to be positively grounded

Evidence of incorrect handling will invalidate the warranty. All devices are provided with internal protection circuits to the gate electrodes (i.e. all CCD pins except SS, DD, RD, OD and OS) but not to the other pins.

The devices are assembled in a clean room environment. e2v technologies recommend that similar precautions are taken to avoid contaminating the active surface.

# HIGH ENERGY RADIATION

Performance parameters will begin to change if the device is subject to ionising radiation. Characterisation data is held at e2v technologies with whom it is recommended that contact be made if devices are to be operated in any high radiation environment.

## **TEMPERATURE RANGE**

Operating temperature range 153 - 323 K

Storage temperature range 143 - 373 K

Full performance is only guaranteed at the nominal operating temperature of 248 K.

Operation or storage in humid conditions may give rise to ice on the surface when the sensor taken to low ambient temperatures, thereby causing irreversible damage.

Maximum rate of heating or cooling: 5 K/min.